EP1C6Q240C8N IC FPGA 185 E/S 240QFP

Paràmetre del producte

Descripció

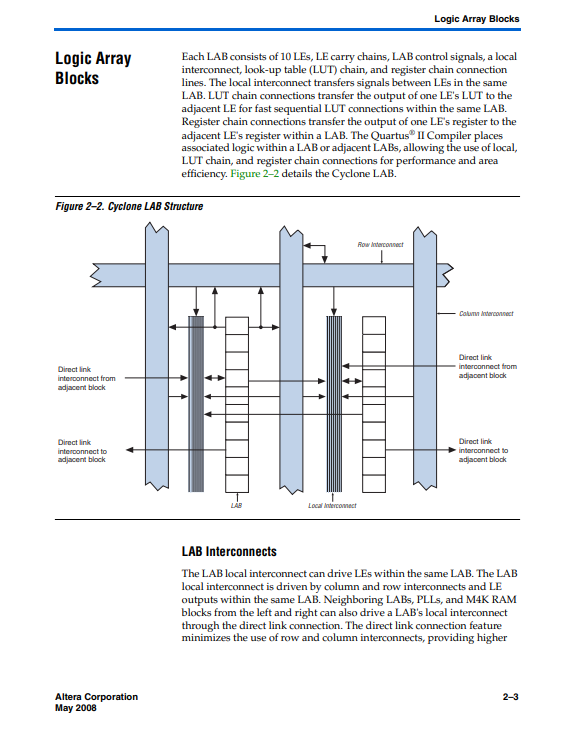

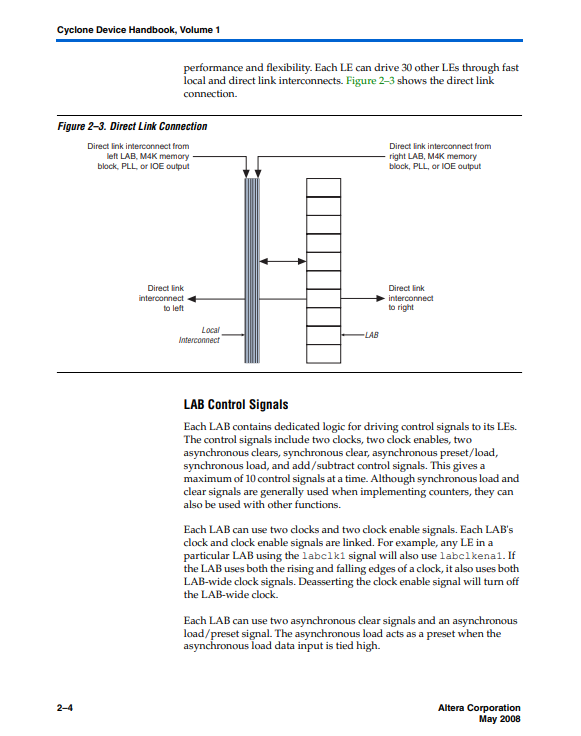

Els dispositius Cyclone® contenen una arquitectura bidimensional basada en files i columnes per implementar una lògica personalitzada.Les interconnexions de columnes i files de velocitats variables proporcionen interconnexions de senyal entre LAB i blocs de memòria incrustats.La matriu lògica consta de LAB, amb 10 LE a cada LAB.Un LE és una petita unitat de lògica que proporciona una implementació eficient de les funcions lògiques de l'usuari.Els LAB s'agrupen en files i columnes a tot el dispositiu.Els dispositius cicló oscil·len entre 2.910 i 20.060 LE.Els blocs RAM M4K són veritables blocs de memòria de doble port amb 4K bits de memòria més paritat (4.608 bits).Aquests blocs proporcionen una memòria dedicada de doble port, de doble port simple o d'un sol port de fins a 36 bits d'ample fins a 250 MHz.Aquests blocs s'agrupen en columnes a través del dispositiu entre determinats LAB.Els dispositius Cyclone ofereixen entre 60 i 288 Kbits de RAM incrustada.Cada pin d'E/S del dispositiu Cyclone s'alimenta d'un element d'E/S (IOE) situat als extrems de les files i columnes LAB al voltant de la perifèria del dispositiu.Els pins d'E/S admeten diversos estàndards d'E/S diferencials i unilaterals, com ara l'estàndard PCI de 66 i 33 MHz, 64 i 32 bits i l'estàndard d'E/S LVDS de fins a 640 Mbps.Cada IOE conté un buffer d'E/S bidireccional i tres registres per registrar els senyals d'entrada, sortida i sortida.Els pins DQS, DQ i DM de doble propòsit juntament amb les cadenes de retard (utilitzades per alinear els senyals de fase DDR) proporcionen suport d'interfície amb dispositius de memòria externa com ara DDR SDRAM i dispositius FCRAM de fins a 133 MHz (266 Mbps).Els dispositius Cyclone proporcionen una xarxa de rellotge global i fins a dos PLL.La xarxa de rellotge global consta de vuit línies de rellotge global que circulen per tot el dispositiu.La xarxa de rellotge global pot proporcionar rellotges per a tots els recursos del dispositiu, com ara IOE, LE i blocs de memòria.Les línies de rellotge global també es poden utilitzar per a senyals de control.Els PLL de cicló proporcionen un rellotge de propòsit general amb multiplicació de rellotge i canvi de fase, així com sortides externes per a suport d'E/S diferencial d'alta velocitat.

| Especificacions: | |

| Atribut | Valor |

| Categoria | Circuits integrats (CI) |

| Incrustat - FPGA (Field Programmable Gate Array) | |

| Mfr | Intel |

| Sèrie | Cyclone® |

| paquet | Safata |

| Estat de la part | Obsolet |

| Nombre de LAB/CLB | 598 |

| Nombre d'elements lògics/cel·les | 5980 |

| Bits de RAM totals | 92160 |

| Nombre d'E/S | 185 |

| Tensió - Alimentació | 1,425 V ~ 1,575 V |

| Tipus de muntatge | Muntatge en superfície |

| Temperatura de funcionament | 0 °C ~ 85 °C (TJ) |

| Paquet / estoig | 240-BFQFP |

| Paquet de dispositius del proveïdor | 240-PQFP (32 x 32) |

| Número de producte base | EP1C6 |

RelacionatsPRODUCTES

-

Tel

-

Correu electrònic

-

skype

-

què tal

què tal